# XL2400T 使用说明

## XL2400T User Manual

v1.0

2025.04

深圳市芯岭技术有限公司

[www.xinlinggo.com](http://www.xinlinggo.com)

## 版本

| Version | Date     | Write | Appove | Description |

|---------|----------|-------|--------|-------------|

| V1.0    | 2025/4/1 |       |        | 首次发行        |

|         |          |       |        |             |

|         |          |       |        |             |

|         |          |       |        |             |

|         |          |       |        |             |

## 目录

|      |                      |    |

|------|----------------------|----|

| 1    | 概述                   | 4  |

| 2    | 主要特性                 | 4  |

| 3    | 主要电特性                | 5  |

| 4    | 极限最大额定值              | 7  |

| 5    | 系统结构方框图              | 7  |

| 6    | 引脚定义                 | 8  |

| 7    | 芯片工作状态               | 8  |

| 7.1  | 休眠模式                 | 10 |

| 7.2  | 待机模式-I ( STB1 )      | 10 |

| 7.3  | 待机模式-III ( STB3 )    | 10 |

| 7.4  | 待机模式-II ( STB2 )     | 10 |

| 7.5  | 接收模式                 | 11 |

| 7.6  | 发射模式                 | 11 |

| 8    | 数据通信模式               | 11 |

| 8.1  | 普通模式                 | 12 |

| 8.2  | 增强模式                 | 12 |

| 8.3  | 增强发送模式               | 12 |

| 8.4  | 增强接收模式               | 13 |

| 8.5  | 增强模式下的数据包识别          | 13 |

| 8.6  | 增强模式下的接收端一对多通信       | 14 |

| 8.7  | 中断引脚                 | 16 |

| 9    | SPI 控制接口             | 16 |

| 10   | 控制寄存器                | 16 |

| 11   | 数据包格式描述              | 27 |

| 12   | 典型应用电路 (参考)          | 28 |

| 13   | 印制天线设计 (参考)          | 29 |

| 13.1 | 印制板天线 layout 设计      | 29 |

| 13.2 | Dongle 端的 PIFA 天线设计  | 29 |

| 13.3 | 遥控器控制板的中尺寸 PIFA 天线设计 | 30 |

| 13.4 | 无线鼠标板及遥控器的单极天线设计     | 31 |

| 14   | 芯片封装信息               | 31 |

| 15   | 注意事项                 | 32 |

| 16   | 防护注意事项               | 33 |

## 1 概述

XL2400T 系列芯片是工作在 2.400~2.483GHz 世界通用 ISM 频段的单片无线收发芯片。该芯片集成射频收发机、频率收生器、晶体振荡器、调制解调器等功能模块，并且支持一对多组网和带 ACK 的通信模式。发射输出功率、工作频道以及通信数据率均可配置。芯片已将多颗外围贴片阻容感器件集成到芯片内部。容易过 FCC 等认证。

典型应用领域：

- 无线鼠标键盘

- 电视和机顶盒遥控器

- 无线游戏手柄

- 遥控玩具

- 有源无线标签

- 智能家居及安防系统

## 2 主要特性

➤ 功耗较低

发射模式 (0dBm) 工作电流 6.97mA; 接收模式工作电流 8.83mA; 休眠电流 1.53uA。

➤ 节省外围器件

支持外围 4 个元器件，包括 1 颗晶振和 3 个贴片电容；

支持双层或单层印制板设计，可以使用印制板微带天线；

芯片自带部分链路层的通信协议；配置少量的参数寄存器，使用方便。

➤ 性能优异

125K / 250K / 1M / 2M bps 模式的接收灵敏度为 -96.5 / -95 / -92 / -90dBm；

发射输出功率最大可达 13dBm；

抗干扰性好，接收滤波器的邻道抑制度高，接收机选择性好。容易过 FCC 等认证。

➤ 三/四线 SPI 接口通信/I2C 接口通信

➤ SPI 接口速率最高支持 4Mbps

➤ 支持最大数据长度为 128 字节 (4 级 FIFO)

➤ SOP8 封装

➤ 1M / 2Mbps 模式，需要晶振精度  $\pm 40\text{ppm}$  &  $C_L = 12\text{pF}$

125K/250kbps 模式，需要晶振精度  $\pm 20\text{ppm}$  &  $C_L = 12\text{pF}$

BLE 广播包模式，需要晶振精度  $\pm 10\text{ppm}$  &  $C_L = 12\text{pF}$

➤ 工作电压支持 1.7~3.6V；

➤ 工作温度支持 -40~+125°C

➤ GFSK 通信方式

➤ 支持自动应答及自动重传

### 3 主要电特性

| 特性                | 测试条件( $V_{CC} = 3V \pm 5\%$ , $TA=25^\circ C$ ) | 参数值   |       |      | 单位   |

|-------------------|-------------------------------------------------|-------|-------|------|------|

|                   |                                                 | 最小    | 典型    | 最大   |      |

| ICC               | 休眠模式                                            |       | 1     |      | uA   |

|                   | 待机模式 1                                          |       | 24.2  |      | uA   |

|                   | 待机模式 2                                          |       | 1.18  |      | mA   |

|                   | 发射模式 (-24dBm)                                   |       | 9     |      | mA   |

|                   | 发射模式 (-18dBm)                                   |       | 9.5   |      | mA   |

|                   | 发射模式 (0dBm)                                     |       | 13.7  |      | mA   |

|                   | 发射模式 (2dBm)                                     |       | 17    |      | mA   |

|                   | 发射模式 (8dBm)                                     |       | 25    |      | mA   |

|                   | 接收模式 (250Kbps)                                  |       | 12.3  |      | mA   |

|                   | 接收模式 (1Mbps)                                    |       | 12.3  |      | mA   |

|                   | 接收模式 (2Mbps)                                    |       | 12.3  |      | mA   |

| 系统指标              |                                                 |       |       |      |      |

| $f_{OP}$          | 工作频率                                            | 2400  |       | 2483 | MHz  |

| $PLL_{res}$       | 锁相环频率步径                                         |       | 1     |      | MHz  |

| $f_{XTAL}$        | 晶振频率, 负载电容 12pF                                 |       | 16    |      | MHz  |

| DR                | 码率                                              | 0.125 |       | 2    | Mbps |

| $\Delta f_{250K}$ | 调制频偏@250Kbps                                    |       | 160   | 250  | KHz  |

| $\Delta f_{1M}$   | 调制频偏@1Mbps                                      |       | 160   | 250  | KHz  |

| $\Delta f_{2M}$   | 调制频偏@2Mbps                                      |       | 320   |      | KHz  |

| $FCH_{250K}$      | 频道间隔@250Kbps                                    |       | 1     |      | MHz  |

| $FCH_{1M}$        | 频道间隔@1Mbps                                      |       | 1     |      | MHz  |

| $FCH_{2M}$        | 频道间隔@2Mbps                                      |       | 2     |      | MHz  |

| 发射模式指标            |                                                 |       |       |      |      |

| PRF               | 典型输出功率                                          |       | 0     |      | dBm  |

| PRFC              | 输出功率范围                                          | -24   |       | 8    | dBm  |

| PBW1              | 发射带数据调制的 20dB 带宽 (250Kbps)                      |       | 1     |      | MHz  |

| PBW2              | 发射带数据调制的 20dB 带宽 (1Mbps)                        |       | 1     |      | MHz  |

| PBW3              | 发射带数据调制的 20dB 带宽 (2Mbps)                        |       | 2     |      | MHz  |

| 接收模式指标 (注 1)      |                                                 |       |       |      |      |

| $RX_{max}$        | 误码率<0.1%时的最大接收幅度                                |       | 0     |      | dBm  |

| RXSENS1           | 接收灵敏度 (0.1%BER)                                 |       | -96.5 |      | dBm  |

|                    |                              |         |     |         |     |

|--------------------|------------------------------|---------|-----|---------|-----|

|                    | @125 Kbps                    |         |     |         |     |

| RXSENS2            | 接收灵敏度 (0.1%BER)<br>@250 Kbps |         | -95 |         | dBm |

| RXSENS3            | 接收灵敏度 (0.1%BER)<br>@1Mbps    |         | -92 |         | dBm |

| RXSENS4            | 接收灵敏度 (0.1%BER)<br>@2Mbps    |         | -90 |         | dBm |

| 接收模式邻道选择性          |                              |         |     |         |     |

| C/I <sub>CO</sub>  | 同频的通道选择性@250kbps             |         | 2   |         | dBc |

| C/I <sub>1ST</sub> | 第 1 相邻道选择性@250kbps           |         | -8  |         | dBc |

| C/I <sub>2ND</sub> | 第 2 相邻道选择性@250kbps           |         | -18 |         | dBc |

| C/I <sub>3RD</sub> | 第 3 相邻道选择性@250kbps           |         | -24 |         | dBc |

| C/I <sub>4TH</sub> | 第 4 相邻道选择性@250kbps           |         | -28 |         | dBc |

| C/I <sub>5TH</sub> | 第 5 相邻道选择性@250kbps           |         | -32 |         | dBc |

| C/I <sub>6TH</sub> | 第 6 相邻道选择性@250kbps           |         | -35 |         | dBc |

| C/I <sub>CO</sub>  | 同频的通道选择性@1Mbps               |         | 10  |         | dBc |

| C/I <sub>1ST</sub> | 第 1 相邻道选择性@1Mbps             |         | 1   |         | dBc |

| C/I <sub>2ND</sub> | 第 2 相邻道选择性@1Mbps             |         | -18 |         | dBc |

| C/I <sub>3RD</sub> | 第 3 相邻道选择性@1Mbps             |         | -23 |         | dBc |

| C/I <sub>4TH</sub> | 第 4 相邻道选择性@1Mbps             |         | -28 |         | dBc |

| C/I <sub>5TH</sub> | 第 5 相邻道选择性@1Mbps             |         | -32 |         | dBc |

| C/I <sub>6TH</sub> | 第 6 相邻道选择性@1Mbps             |         | -35 |         | dBc |

| C/I <sub>CO</sub>  | 同频的通道选择性@2Mbps               |         | 10  |         | dBc |

| C/I <sub>1ST</sub> | 第 1 相邻道选择性@2Mbps             |         | -6  |         | dBc |

| C/I <sub>2ND</sub> | 第 2 相邻道选择性@2Mbps             |         | -10 |         | dBc |

| C/I <sub>3RD</sub> | 第 3 相邻道选择性@2Mbps             |         | -22 |         | dBc |

| C/I <sub>4TH</sub> | 第 4 相邻道选择性@2Mbps             |         | -28 |         | dBc |

| C/I <sub>5TH</sub> | 第 5 相邻道选择性@2Mbps             |         | -34 |         | dBc |

| 操作条件               |                              |         |     |         |     |

| VDD                | 供电电压                         | 1.7     | 3   | 3.6     | V   |

| VSS                | 芯片地                          |         | 0   |         | V   |

| V <sub>OH</sub>    | 高电平输出电压                      | VDD-0.3 |     | VDD     | V   |

| V <sub>OL</sub>    | 低电平输出电压                      | VSS     |     | VSS+0.3 | V   |

| V <sub>IH</sub>    | 高电平输入电压                      | VDD-0.3 |     | VDD     | V   |

| V <sub>IL</sub>    | 低电平输入电压                      | VSS     |     | VSS+0.3 | V   |

\* 注 1：在晶振 32MHz 的整数倍（如 2416、2432MHz 等）的频道及相邻正负 1MHz 的频道的接收灵敏度退化 2dB；发射信号调制精度（EVM）退化 10%。请使用我们建议信道。

## 4 极限最大额定值

| 特性               | 条件                  | 参数值  |    |     | 单位 |

|------------------|---------------------|------|----|-----|----|

|                  |                     | 最小   | 典型 | 最大  |    |

| 最大额定值            |                     |      |    |     |    |

| V <sub>DD</sub>  | 供电电压                | -0.3 |    | 3.6 | V  |

| V <sub>I</sub>   | 输入电压                | -0.3 |    | 3.6 | V  |

| V <sub>O</sub>   | 输出电压                | VSS  |    | VDD |    |

| P <sub>d</sub>   | 总功耗 (TA=-40°C~85°C) |      |    | 300 | mW |

| T <sub>OP</sub>  | 工作温度                | -40  |    | 125 | °C |

| T <sub>STG</sub> | 存储温度                | -40  |    | 125 | °C |

注：1、使用中强行超过一项或多项极限最大额定值会导致器件永久性损坏。

2、静电敏感器件，操作时遵守防护规则。

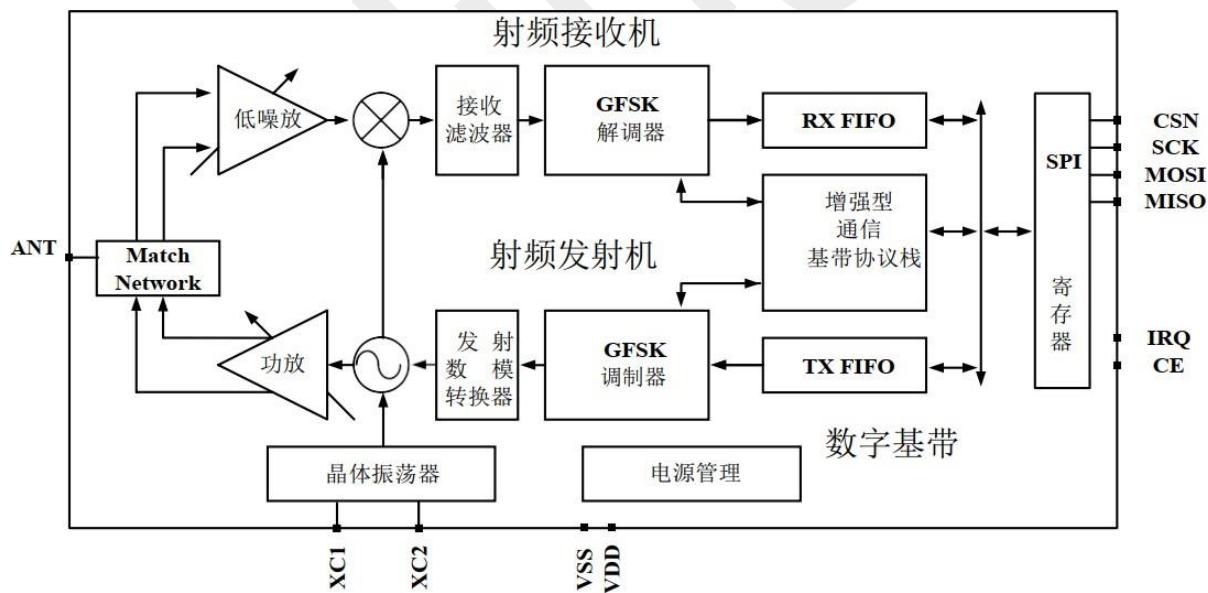

## 5 系统结构方框图

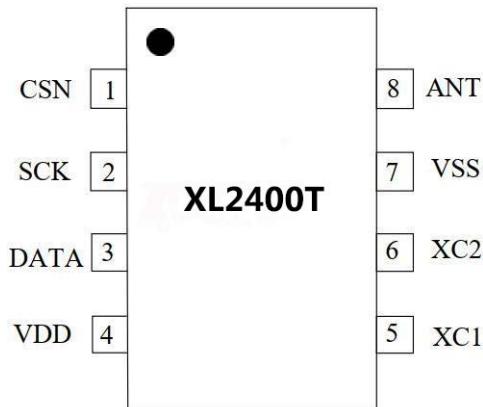

## 6 引脚定义

| 引脚端序号 | 符号   | 功能           | 引脚端序号 | 符号  | 功能       |

|-------|------|--------------|-------|-----|----------|

| 1     | CSN  | SPI 片选信号     | 5     | XC1 | 晶振输入     |

| 2     | SCK  | SPI 时钟信号     | 6     | XC2 | 晶振输出     |

| 3     | DATA | SPI 数据输入输出信号 | 7     | VSS | 地 (GND)  |

| 4     | VDD  | 电源输入         | 8     | ANT | 射频信号输入输出 |

## 7 芯片工作状态

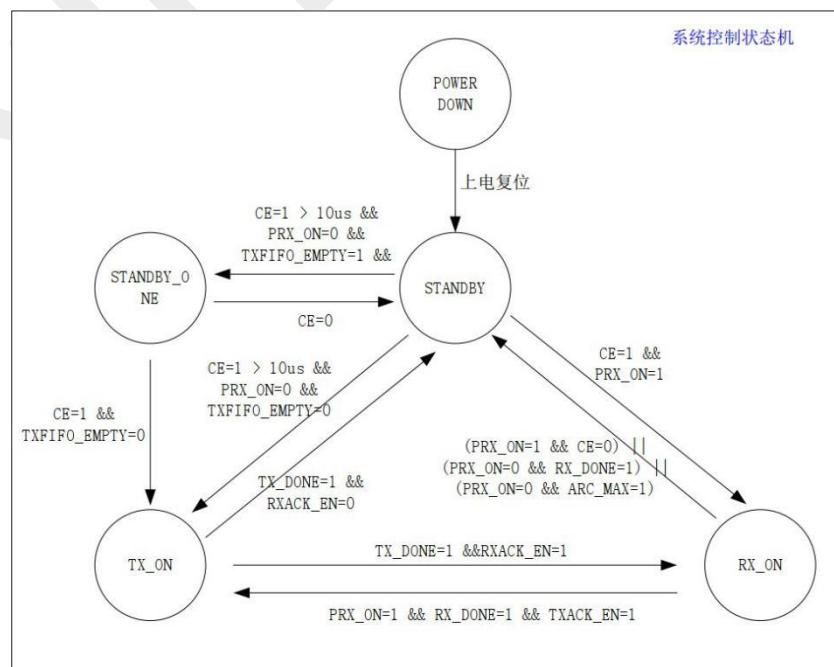

本章描述 XL2400T 系列芯片的各种工作模式，以及用于控制芯片进入各工作模式的方法。XL2400T 芯片自带状态机受控于芯片内部寄存器的配置值和外部引脚信号。

如上是 XL2400T 工作状态图，表示 5 种工作模式之间的跳变。XL2400T 在 VDD 大于 1.7V 才开始正常工作。即使进入休眠模式，MCU 还是可以通过 SPI 发送配置命令及 CE 管脚使芯片进入其它 5 种状态。

如上所示，系统包括 5 个主要状态，分别如下：

1. POWER DOWN。数字系统断电状态。

2. STANDBY。系统上电后自动进入该状态。

3. STANDBY ONE。当配置为 PTX 器件，且 CE=1 持续时间大约 10us，且 TXFIFO 中没有数据，系统进入该状态，等待发送数据。

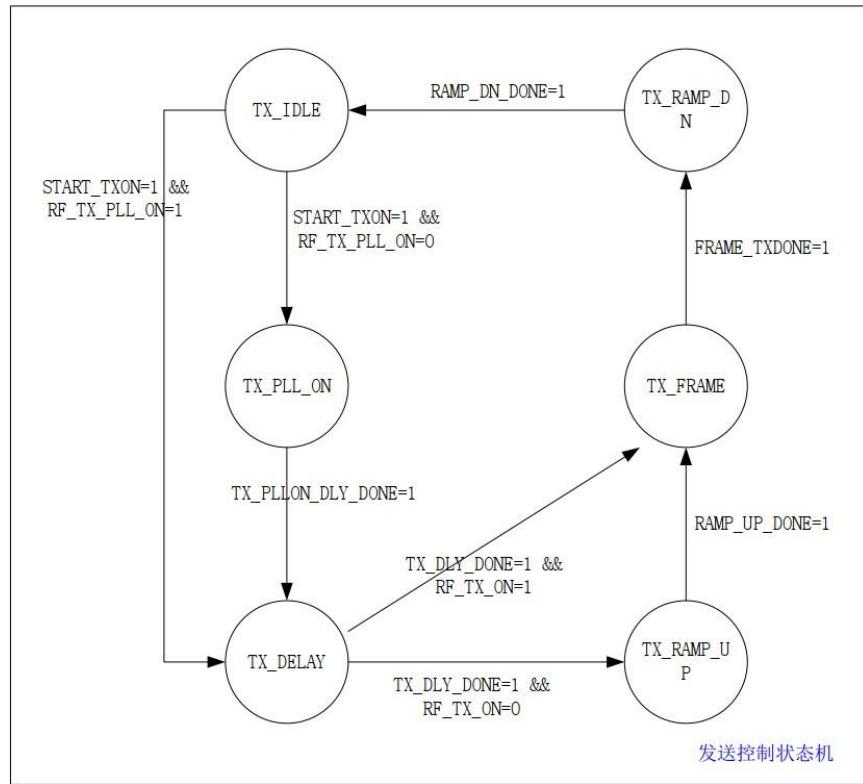

4. TX ON。当配置为 PTX 器件，且 CE=1 持续时间大约 10us，且 TXFIFO 中有数据，系统进入该状态。在该状态下完成数据的发送处理，系统会启动发送控制状态机进行工作，直到数据发送完成。若配置自动ACK 接收，则系统会进入RX ON 状态开始接收 ACK。

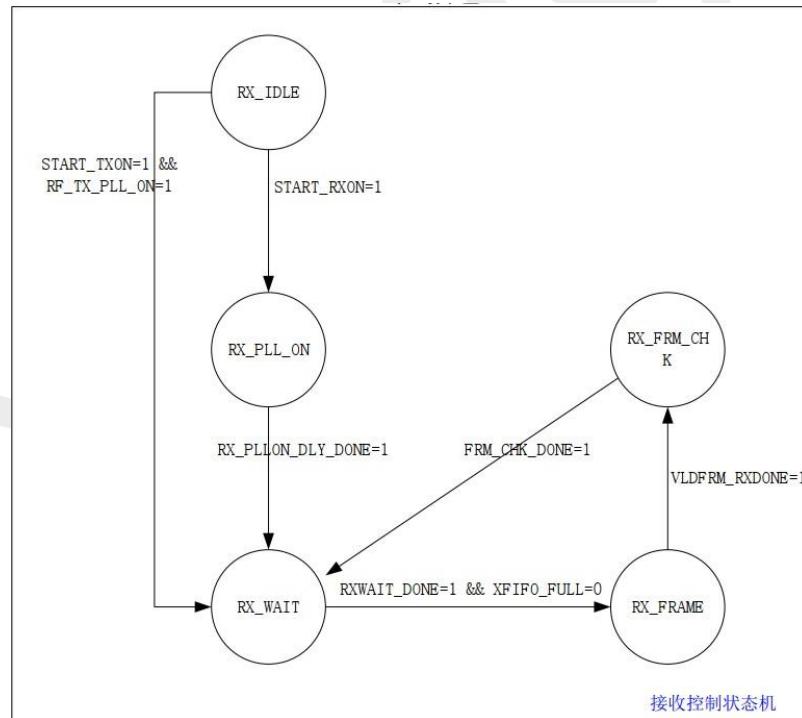

5. RX ON。当配置为 PRX 器件，且 CE=1 时，系统进入该状态。在该状态下完成数据的接收处理，系统会启动接收控制状态机进行工作，直到接收到一个帧。当配置自动 ACK 发送，则系统会就进入 TX ON 状态发送 ACK。若 PTX 器件有效，且自动 ACK 接收使能，则还会启动发送重传。

## 7.1 休眠模式

在休眠模式下，XL2400T 所有功能关闭，保持电流消耗最小。进入休眠模式后，XL2400T 停止工作，但寄存器内容保持不变。休眠模式由寄存器中 PWR\_UP 位控制。

## 7.2 待机模式-I ( STB1 )

在待机模式-I 下，芯片维持晶振振荡但不输出其管脚模块，其余功能模块均关闭，消耗电流较小。在休眠模式下，通过配置寄存器 PWR\_UP 的值为 1，芯片即可进入待机模式-I。而处于发射或接收模式时，可以通过配置 CE 和 EN\_PM 控制信号为 0，芯片返回到待机模式-I。

## 7.3 待机模式-III ( STB3 )

在待机模式-I 时，配置 EN\_PM 控制信号为 1，芯片进入到待机模式-III。待机模式-III 主要目的是使得芯片的电源管理模块启动和输出高速时钟。

## 7.4 待机模式-II ( STB2 )

收送端 TX FIFO 寄存器为空并且 CE 引脚置 1，进入入待机模式-II (待机模式-II 通常可以理解为预备发射模式)。此时，晶振有较强的输出驱动能力且芯片的电源管理模块开启。待机模式-II 下，如果有数据包送入 TX FIFO，此时芯片内部锁相环立刻启动工作并且经过一段锁相环的锁定时间后，发射机将数据包发出去。

## 7.5 接收模式

当 PWR\_UP、PRIM-RX、EN\_PM、CE 置 1 时，进入接收模式。

在 RX 模式下，射频部分接收从天线来的信号，将其放大、下变频、滤波和解调，根据地址、校验码、数据长度等，判断是否收包有效，有效收包上传 RX FIFO，上报中断。如果 RX FIFO 是满的，接收的数据包就会被丢弃。

## 7.6 发射模式

当 PWR\_UP、EN\_PM 置 1，PRIM-RX 置 0，CE 置 1，且 TX FIFO 中存在有效数据，进入发射模式。

XL2400T 在数据包发送完之前都会保持在发送模式。发送完成后，返回到待机模式。XL2400T 支持连续发包和发长包模式。

## 8 数据通信模式

XL2400T 芯片搭配 MCU 来共同完成通信功能。链路层，如数据组帧、校验、地址判断、数据白化的扰码、数据重传和 ACK 响应等处理是由芯片内部完成的，无需 MCU 参与。

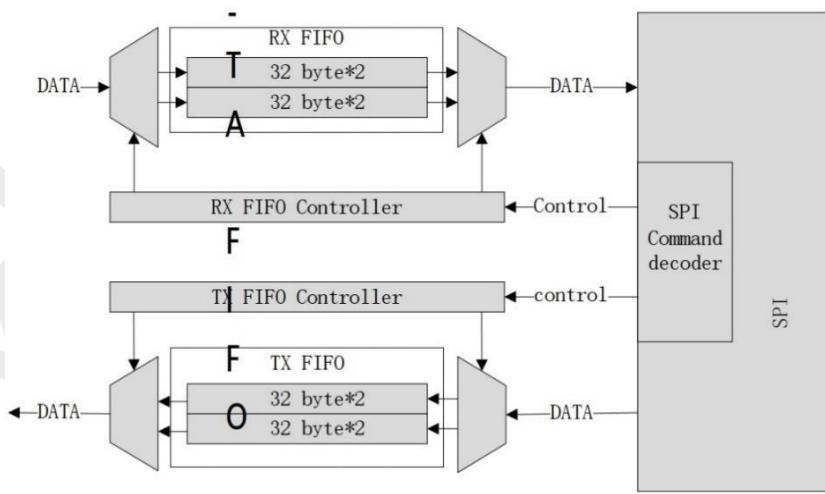

XL2400T 芯片可配置为四个不同的 RX FIFO 寄存器（32 字节）或者一个 RX FIFO 寄存器（128 字节）（6 个接收通道共享）、四个不同的 TX FIFO 寄存器（32 字节）或者一个 TX FIFO 寄存器（128 字节）。在休眠模式和待机模式下，MCU 可以访问 FIFO 寄存器。

XL2400T 芯片主要有两种数据通信模式：

- 不带自动重传不带ACK 的通信模式（后简称为普通模式），发射端可以使用命令有 W\_TX\_PAYLOAD, REUSE\_TX\_PL 等；

- 带自动重传带ACK 的通信模式（后简称为增强模式），发射端可以使用命令有 W\_TX\_PAYLOAD, W\_TX\_PAYLOAD\_NOACK, REUSE\_TX\_PL 等；接收端可以使用命令有 W\_ACK\_PAYLOAD 等；

### 普通模式

| 通信名称              | 普通模式      |      |

|-------------------|-----------|------|

| 通信方               | PTX       | PRX  |

| 特点                | 单向发送      | 单向接收 |

| 收送数据的组帧方式         | I         | 无    |

| 开启 REUSE_TX_PL 命令 | 重复发送前一包数据 | 无    |

### 增强模式

| 通信名称 | 增强模式           |               |

|------|----------------|---------------|

| 通信方  | PTX            | PRX           |

| 特点   | 发送数据后，等待接收 ACK | 接收数据后，回收送 ACK |

|                                                   |                           |                                  |

|---------------------------------------------------|---------------------------|----------------------------------|

| 发送数据的组帧方式                                         | 发送数据组帧方式 II               | 回发送 ACK 组帧方式 III                 |

| PTX 使用 REUSE_TX_PL 命令                             | 重复发送前一包数据                 | 每收到一包，回发送 ACK                    |

| PTX 使用 W_TX_PAYLOAD 命令<br>PRX 使用 W_ACK_PAYLOAD 命令 | 发送数据后，等待接收 ACK<br>PAYLOAD | 接收数据后，回发送 ACK<br>PAYLOAD，组帧方式 II |

| PTX 使用 W_TX_PAYLOAD_NO_ACK 命令                     | 发送一次数据，不等 ACK，组帧方式 II     | 接收数据，不回 ACK                      |

## 8.1 普通模式

普通模式下，发送端从 TX FIFO 寄存器中取出数据并且发送，发送完成后上报中断（中断需要清除），同时 TX FIFO 寄存器清除该数据（TX FIFO 需要清空）；接收端接收到有效的地址和数据时上报中断通知 MCU，随后 MCU 可将该数据从 RX FIFO 寄存器中读。TX FIFO 和 RX FIFO 需要清空，中断需要清除）。

普通模式，(0X01) EN\_AA 寄存器置 0X00, (0X04) SETUP\_RETR 寄存器置 0X00, (0X1C) DYNPD 寄存器置 0X00, (0X1D) FEATURE 寄存器的低 3 bit 置 000。

## 8.2 增强模式

增强模式下，把主动发起通信的一方称为 PTX（主发端），把接收数据并响应的一方称为 PRX（主收端）。PTX 发出数据后等待应答信号，PRX 接收到有效数据后回应应答信号。PTX 规定时间内未收到应答信号，自动重新发送数据。自动重传和自动应答功能为 XL2400T 芯片自带，无需 MCU 参与。

PTX 在发送数据后自动转到接收模式等待应答信号。如果没有在规定时间内收到正确的应答信号，PTX 将重发相同的数据包，直到收到应答信号，或传输次数超过 ARC 的值（SETUP\_RETR 寄存器）产生 MAX\_RT 中断。PTX 收到应答信号，即认为数据已经发送成功（PRX 收到有效数据），清除 TX FIFO 中的数据并产生 TX\_DS 中断（TX FIFO 和 RX FIFO 需要清空，中断需要清除）。

PRX 每次收到一包有效数据都会回 ACK 应答信号，该数据如果为新数据（PID 值与上一包数据不同）保存到 RX FIFO，否则就丢弃。

增强模式，需要保证 PTX 的 TX 地址（TX\_ADDR）、通道 0 的 RX 地址（如 RX\_ADDR\_P0），以及 PRX 的 RX 地址（如 RX\_ADDR\_P5）三者相同。例：在图 5 中，PTX5 对应 PRX 的数据通道 5，地址设置如下：

PTX5: TX\_ADDR=0xC2C3C4C5C1

PTX5: RX\_ADDR\_P0=0xC2C3C4C5C1

PRX: RX\_ADDR\_P5=0xC2C3C4C5C1

增强模式有如下特征：

- 减少 MCU 的控制，简化软件操作；

- 抗干扰能力强，减少无线传输中因瞬间同频干扰造成的丢包，更易开发跳频算法；

- 重传过程中，减少 MCU 通过 SPI 接口的每次写入待发送数据的操作时间。

## 8.3 增强发送模式

1、CE 置 0，CONFIG 寄存器的 PRIM\_RX 位先置 0。

2、当发送数据时，发送地址（TX\_ADDR）和有效数据（TX\_PLD）通过 SPI 接口按字节写入地址寄存器

和 TX FIFO。CSN 引脚为低时，数据写入，CSN 引脚再次为高，数据完成写入。

3、CE 从 0 置 1，启动发射 (CE 至少持续置 1 在 30us 以上，该操作生效)。

4、自动应答模式下 (SETUP\_RTR 寄存器置不为 0, ENAA\_P0=1)，PTX 发送完数据后立即自动将通道 0 切换到接收模式等待应答信号。如果在有效应答时间范围内收到 ACK 应答信号，则认为数据发送成功，状态寄存器的 TX\_DS 位置 1 并自动清除 TX FIFO 中的数据。如果在设定时间范围内没有接收到应答信号，则自动重传数据。

5、如果自动传输计数器 (ARC\_CNT) 溢 (超过了设定值)，则状态寄存器的 MAX\_RT 位置 1，不清除 TX FIFO 中的数据。当 MAX\_RT 或 TX\_DS 为 1 时，IRQ 引脚产生低电平中断 (需要使能相应中断)。中断可以通过写状态寄存器来复位。

6、数据包丢失计数器 (PLOS\_CNT) 在每次产生 MAX\_RT 中断后加一。自动传输计数器 ARC\_CNT 统计重发数据包的次数；数据包丢失计数器 PLOS\_CNT 统计在达到最大允许传输次数时仍没有发送成功的数据包个数。

7、产生 MAX\_RT 或 TX\_DS 中断后，系统进入待机模式。

## 8.4 增强接收模式

1、CE 置 0，CONFIG 寄存器的 PRIM\_RX 位先置 1。准备接收数据的通道必须被使能 (EN\_RXADDR 寄存器)，所有工作在增强型通信模式下的数据通道的自动应答功能是由 EN\_AA 寄存器来使能的，有效数据宽度是由 RX\_PWD\_PX 寄存器来设置的。

2、接收模式由设置 CE 为 1 启动。

3、预设的等待时间后，PRX 开始检测无线信号。

4、接收到有效的数据包后，数据存储在 RX\_FIFO 中，同时 RX\_DR 位置 1，产生中断。状态寄存器中 RX\_P\_NO 位显示数据是由哪个通道接收到的。

5、自动收送 ACK 应答信号。

6、如果 CE 保持为 1，继续进入接收模式；如果 CE 置为 0，则进入待机模式-III；

7、MCU 以合适的速率通过 SPI 口将数据读。

## 8.5 增强模式下的数据包识别

## PID 生成和检测

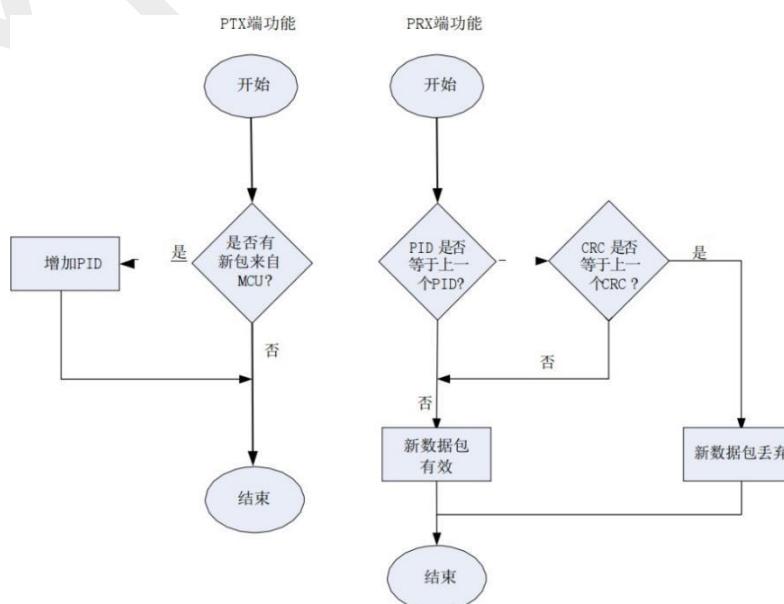

每一包数据都包括两位的 PID (数据包标志位), 来帮助接收端识别该数据是新数据包还是重发的数据包, 防止多次存入相同的数据包, PID 的生成和检测如图所示。发送端从 MCU 取得一包新数据后 PID 值加一。

## 8.6 增强模式下的接收端一对多通信

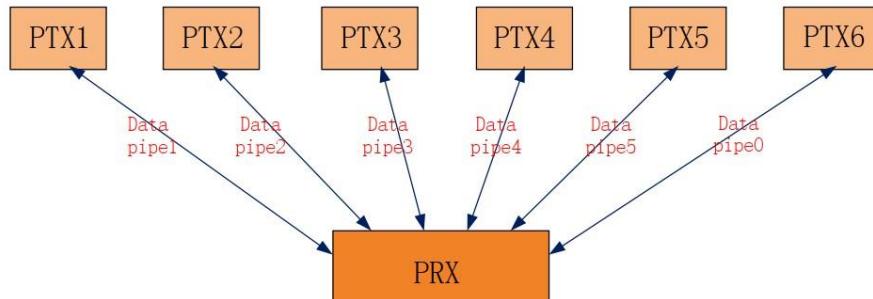

XL2400T 芯片作为发射端, 对于一对多通信, 可以采用不同的地址不多个接收端进行通信。XL2400T 芯片作为接收端, 可以接收 6 路不同地址、相同频率的发送端数据。每个数据通道拥有自己的地址。

使能哪些数据通道是通过寄存器 EN\_RXADDR 来设置的。每个数据通道的地址是通过寄存器 RX\_ADDR\_PX 来配置的。通常情况下不允许不同的数据通道设置完全相同的地址。如下表给了一例多接收通道地址配置的示例。

|                         | Byte 4 | Byte 3 | Byte 2 | Byte 1 | Byte 0 |

|-------------------------|--------|--------|--------|--------|--------|

|                         |        |        |        |        |        |

| Data pipe 0(RX_ADDR_P0) | 0xF1   | 0xD2   | 0xE6   | 0xA2   | 0x33   |

|                         |        |        |        |        |        |

| Data pipe 1(RX_ADDR_P1) | 0xD3   | 0xD3   | 0xD3   | 0xD3   | 0xD3   |

|                         | ↓      | ↓      | ↓      | ↓      |        |

| Data pipe 2(RX_ADDR_P2) | 0xD3   | 0xD3   | 0xD3   | 0xD3   | 0xD4   |

|                         | ↓      | ↓      | ↓      | ↓      |        |

| Data pipe 3(RX_ADDR_P3) | 0xD3   | 0xD3   | 0xD3   | 0xD3   | 0xD5   |

|                         | ↓      | ↓      | ↓      | ↓      |        |

| Data pipe 4(RX_ADDR_P4) | 0xD3   | 0xD3   | 0xD3   | 0xD3   | 0xD6   |

|                         | ↓      |        | ↓      | ↓      |        |

| Data pipe 5(RX_ADDR_P5) | 0xD3   | 0xD3   | 0xD3   | 0xD3   | 0xD7   |

从表中可以看出数据通道 0 的 5byte 总共 40 位的地址都是可配的; 数据通道 1~5 的地址配置为 32 位共用地址 (不数据通道 1 共用) +8 位各自的地址 (最低字节)。

XL2400T 芯片在接收模式下可以不最多 6 路不同通道通信, 如图所示。每一个数据通道使用不同的地址, 共用相同的频道。所有的发射端和接收端设置为增强模式。

PRX 在接收到有效数据后记录 PTX 的 TX 地址, 并以此地址为目标地址发送应答信号。PTX 数据通道 0 被用做接收应答信号时, 数据通道 0 的 RX 地址要与 TX 地址相等以确保接收到正确的应答信号。下图给了 PTX 和 PRX 地址如何配置的例子。

TX\_ADDR:0XC2C3C4C5E2 TX\_ADDR:0XC2C3C4C5EF TX\_ADDR:0XC2C3C4C5E4 TX\_ADDR:0XC2C3C4C5D1 TX\_ADDR:0XC2C3C4C5C1 TX\_ADDR:0XCF3E410F02

RX\_ADDR:0XC2C3C4C5E2 RX\_ADDR:0XC2C3C4C5EF RX\_ADDR:0XC2C3C4C5E4 RX\_ADDR:0XC2C3C4C5D1 RX\_ADDR:0XC2C3C4C5C1 RX\_ADDR:0XCF3E410F02

多通道数据传输应答地址示例

## 7.7 D

A

FIFO 框图

XL2400T 包含发 TX\_FIFO, RX\_FIFO。通过 SPI 命令可读写 FIFO。在发送模式下通过 W\_TX\_PAYLOAD 和 W\_TX\_PAYLOAD\_NO\_ACK 指令来写 TX\_FIFO。如果产生 MAX\_RT 中断，在 TX\_FIFO 中的数据不会被清除。在接收模式下通过 R\_RX\_PAYLOAD 指令读取 RX\_FIFO 中的 payload, R\_RX\_PL\_WID 指令读取 payload 的长度。FIFO\_STATUS 寄存器指示 FIFO 的状态。

## 8.7 中断引脚

对于 SOP8 封装，中断状态靠查询 STATUS 寄存器方式来获取。

对于非 SOP8 封装，XL2400T 芯片的中断引脚（IRQ）为低电平触发，IRQ 引脚初始状态为高电平，当状态寄存器中 TX\_DS、RX\_DR 或 MAX\_RT 为 1，以及相应的中断上报使能位为 0 时，IRQ 引脚的中断触发。MCU 给相应中断源写 ‘1’ 时，清除中断。IRQ 引脚的中断触发可以被屏蔽或者使能，通过设置中断上报使能位为 1，禁止 IRQ 引脚的中断触发。

## 9 SPI 控制接口

如有读的命令操作（包括 R\_REGISTER、R\_RX\_PAYLOAD、R\_RX\_PL\_WID 三条命令），DATA 引脚先为输入状态，在 SCK 信号的第八个时钟下降沿自动切换为输出状态，并且在后续时钟上升沿输出信号；要求 MCU 的对应 DATA 引脚的 GPIO，在 SCK 信号的第八个时钟上升沿的保持时间后，从输出状态转为输入状态。

需要 CE\_SEL 设为 1，启动命令方式控制；CE\_L\_sel 设为 1，将 CE 的 GPIO 弱下拉电阻使能；使用 CE\_FSP[1]\_ON/CE\_FSP[1]\_OFF 命令方式控制 CE 状态。

中断状态靠查询 STATUS 寄存器方式来获取。

在发送过程中，采用先在 STB1 或 STB3 状态下修改必要的寄存器，并写入 PAYLOAD；CE high 30us 后 CE low，使得进入发射模式，等待发送完成后（约 1ms）再进行 SPI 读写操作。如在发送过程中，进行 SPI 读写操作会引起电源纹波，影响发射信号的质量。

## 10 控制寄存器

可以通过 SPI 读写操作表中的寄存器，来配置和控制 XL2400T。

| Address (hex) | Name    | Bit | Reset value | Type | Description                   |

|---------------|---------|-----|-------------|------|-------------------------------|

| 00            | CFG_TOP |     |             |      | Top-level configuration       |

|               | EN_PM   | 19  | 0           | R/W  | pmu enable:1 work 0 powerdown |

|  |               |    |   |     |                                                                                                                                                                    |

|--|---------------|----|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | HW_RC_CL_EN   | 18 | 0 | R/W | Hardware RC Calibration<br>0: disable Hardware RC Calibration<br>1: enable Hardware RC Calibration                                                                 |

|  | AJ_FREQ_ACK   | 17 | 1 | R/W | Adjust frequency on ack<br>0: disable adjust frequency on ack<br>1: enable adjust frequency on ack                                                                 |

|  | CE_PD         | 16 | 1 | R/W | CE PAD Pull-Down Enable<br>1: Pull-Down Enable<br>0: Pull-Down Disable                                                                                             |

|  | CE_SEL        | 15 | 0 | R/W | Hardware/Software CE selection<br>0: Hardware CE<br>1: Software CE                                                                                                 |

|  | CE_SOFT       | 14 | 0 | R/W | Software CE                                                                                                                                                        |

|  | DAC_COMP_OUT  | 13 | 0 | R/W | TX IQ output option;<br>1: TX output IQ using complement form<br>0: TX output IQ using true form                                                                   |

|  | WHITEN_OPT    | 12 | 0 | R/W | Whiten option;<br>1: PN9 (CC2500)<br>0: 34B (ssv7241)                                                                                                              |

|  | ADDR_TX_OPT   | 11 | 0 | R/W | Address Send option;<br>1: MSB(msb)--->MSB(lsb), .,LSB(msb)-->LSB(lsb)<br>0: LSB(msb)-->LSB(lsb), .,MSB(msb)-->MSB(lsb)                                            |

|  | IF_2M_SEL     | 10 | 0 | R/W | IF Frequency select;<br>1: 2MHz IF<br>0: 1MHz IF                                                                                                                   |

|  | BPS_IDLE_RST  | 9  | 1 | R/W | Bypass reset during idle state;<br>1: during idle state, just close clock and<br>don't assert reset;<br>0: during idle state, both close clock and<br>assert reset |

|  | BPS_GATED_CLK | 8  | 0 | R/W | Bypass clock gate function;<br>1: during idle state, don't close clock<br>0: during idle state, close clock                                                        |

|  | LOOPBACK_EN   | 7  | 0 | R/W | LoopBack Enable;<br>1: Tx output loopback into ADC input;<br>0: normal mode                                                                                        |

|  | MASK_RX_DR    | 6  | 0 | R/W | Mask interrupt caused by RX_DR;<br>0: interrupt not reflected on IRQ pin; 1:<br>reflect RX_DR as active low<br>interrupt on IRQ pin                                |

|  | MASK_TX_DS    | 5  | 0 | R/W | Mask interrupt caused by TX_DS;<br>0: interrupt not reflected on IRQ pin;                                                                                          |

|    |                 |     |    |     |                                                                                                                                    |

|----|-----------------|-----|----|-----|------------------------------------------------------------------------------------------------------------------------------------|

|    |                 |     |    |     | 1: reflect TX_DS as active low interrupt on IRQ pin                                                                                |

|    | MASK_MAX_RT     | 4   | 0  | R/W | Mask interrupt caused by MAX_RT;<br>0: interrupt not reflected on IRQ pin;<br>1: reflect MAX_RT as active low interrupt on IRQ pin |

|    | EN_CRC          | 3   | 1  | R/W | Enable CRC. <u>Forced high if any of the bits in EN_AA is high</u>                                                                 |

|    | CRCC            | 2   | 0  | R/W | CRC scheme<br>0: 1 byte, 1: 2 bytes                                                                                                |

|    | PWR_ON          | 1   | 0  | R/W | 1: power-up, 0: power-down                                                                                                         |

|    | RX_ON           | 0   | 0  | R/W | 1: PRX, 0: PTX                                                                                                                     |

| 01 | EN_AA           |     |    |     | Auto-acknowledgement settings                                                                                                      |

|    | Reserved        | 7:6 | 0  | R/W | Unused                                                                                                                             |

|    | ENAA_P5         | 5   | 1  | R/W | Enable AA on data pipe 5                                                                                                           |

|    | ENAA_P4         | 4   | 1  | R/W | Enable AA on data pipe 4                                                                                                           |

|    | ENAA_P3         | 3   | 1  | R/W | Enable AA on data pipe 3                                                                                                           |

|    | ENAA_P2         | 2   | 1  | R/W | Enable AA on data pipe 2                                                                                                           |

|    | ENAA_P1         | 1   | 1  | R/W | Enable AA on data pipe 1                                                                                                           |

|    | ENAA_P0         | 0   | 1  | R/W | Enable AA on data pipe 0                                                                                                           |

| 02 | EN_RXADDR       |     |    |     | Enable RX addresses                                                                                                                |

|    | Reserved        | 7:6 | 0  | R/W | Unused                                                                                                                             |

|    | ENRX_P5         | 5   | 0  | R/W | Enable data pipe 5                                                                                                                 |

|    | ENRX_P4         | 4   | 0  | R/W | Enable data pipe 4                                                                                                                 |

|    | ENRX_P3         | 3   | 0  | R/W | Enable data pipe 3                                                                                                                 |

|    | ENRX_P2         | 2   | 0  | R/W | Enable data pipe 2                                                                                                                 |

|    | ENRX_P1         | 1   | 1  | R/W | Enable data pipe 1                                                                                                                 |

|    | ENRX_P0         | 0   | 1  | R/W | Enable data pipe 0                                                                                                                 |

| 03 | SETUP_AW        |     |    |     | Address width & timing stup                                                                                                        |

|    | PLLON_LOCK_TIME | 7:4 | A  | R/W | PLL Locking Time;<br>0: 20us;<br>1: 27.5us;<br>.....<br>F: 132.5us                                                                 |

|    | TX_AW           | 3:2 | 11 | R/W | Address width for PTX;<br>1: 3Byte;<br>2: 4Byte;<br>other: 5Byte                                                                   |

|    | PIPEX_AW        | 1:0 | 11 | R/W | Address width for PRX;<br>1: 3Byte;<br>2: 4Byte;<br>other: 5Byte                                                                   |

| 04 | SETUP_RETR      |     |    |     | Automatic retransmission setup                                                                                                     |

|    |                |       |       |     |                                                                                                                                        |

|----|----------------|-------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

|    | GPIO_CONFIG    | 29:28 | 0x0   | R/W | GPIO Configuration<br>0x0: Input<br>0x1: Output tx_mod_bit<br>0x2: Output rx_dem_bit<br>0x3: Output '0'                                |

|    | GPIO_I_INV     | 27    | 0x0   | R/W | GPIO input invert phase                                                                                                                |

|    | RXDEMOD_BYPASS | 26    | 0x0   | R/W | Rx Demodulate function bypass enable                                                                                                   |

|    | TXFRAME_BYPASS | 24    | 0x0   | R/W | Tx Frame function bypass enable                                                                                                        |

|    | DIAG_TEST_OE   | 24    | 0x0   | R/W | Test Mux Output enable                                                                                                                 |

|    | DIAG_SEL       | 23:16 | 0x0   | R/W | Test Mux config.                                                                                                                       |

|    | TX_TIME3_DELAY | 15:12 | 0x0   | R/W | Delay between PLL openloop timing and Send Data. Unit is 10us                                                                          |

|    | TX_TIME2_DELAY | 11:8  | 0x0   | R/W | Delay between PLL lock timing and PLL openloop timing. Unit is 25us                                                                    |

|    | ARD[3:0]       | 7:4   | 0011  | R/W | Automatic retransmission delay<br>0000: wait 250uS<br>0001: wait 500uS<br>...<br>1111: wait 4000uS<br>Delay defined as “”              |

|    | ARC[3:0]       | 3:0   | 0011  | R/W | Auto retransmit count<br>0000: disabled<br>0001: up to 1 re-transmit on fail of AA<br>...<br>1111: up to 15 re-transmits on fail of AA |

| 05 | RF_CH          |       |       |     | RF channel                                                                                                                             |

|    | RF_PWR         | 21:16 | 0x2C  | R/W | Set RF output power in TX mode, 010000                                                                                                 |

|    | Reserved       | 15:14 | 0     | R/W | Unused                                                                                                                                 |

|    | RF_CH[6:0]     | 13:0  | 0x95B | R/W | Set frequency channel in 1 MHz increment, 0x962 is 2402MHz                                                                             |

| 06 | SETUP_RF       |       |       |     | RF settings                                                                                                                            |

|    | TX_PATTERN     | 15:8  | 0     | R/W | Cyclix Pattern                                                                                                                         |

|    | EN_CW          | 7     | 0     | R/W | Enable continuous carrier when set high<br>Confirm during chip verification                                                            |

|    | BER_EN         | 6     | 0     | R/W | Enable PN9 bit stream when set high;                                                                                                   |

|    | RF_DR_LOW      | 5     | 1     | R/W | See RF_DR_HIGH                                                                                                                         |

|    | TX_ATTN        | 4     | 0     | R/W | TX low-power mode <u>Confirm</u> actual attenuation level                                                                              |

|    | RF_DR_HIGH     | 3     | 0     | R/W | [RF_DR_LOW, RF_DR_HIGH]<br>00: 1Mbps<br>01: 2Mbps<br>10: 250kbps<br>11: 125kbps                                                        |

|    | Reserved       | 2:1   | 0x1   | R   | Unused                                                                                                                                 |

|    |               |       |      |     |                                                                                                                                                               |

|----|---------------|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | CYC_PATT_TXEN | 0     | 0    | R/W | Cyclix Pattern Tx Enable                                                                                                                                      |

| 07 | STATUS        |       |      |     | Status (read-out from SDO pin during SPI command word input); SDO output may be adjusted                                                                      |

|    | Reserved      | 7     | 0    | R/W | Unused                                                                                                                                                        |

|    | RX_DR         | 6     | 0    | R/W | Data ready RX FIFO interrupt. Asserted when new data arrives at RX FIFO. Write 1 to clear bit                                                                 |

|    | TX_DS         | 5     | 0    | R/W | Data sent TX FIFO interrupt. Asserted when packet transmitted. If auto-ACK is activated, this bit is set high only when ACK is received. Write 1 to clear bit |

|    | MAX_RT        | 4     | 0    | R/W | <b>Maximum</b> number of TX retransmit interrupt. Write 1 to clear bit. If MAX_RT is asserted it <b>must</b> be cleared to enable further operation           |

|    | RX_P_NO[2:0]  | 3:1   | 111  | R   | Data pipe number for the payload available for reading from RX_FIFO<br>000~101: data pipe number (0~5)                                                        |

|    | TX_FULL       | 0     | 0    | R   | 0: TX FIFO available<br>1: TX FIFO full                                                                                                                       |

| 08 | OBSERVE_TX    |       |      |     | Transmission observation                                                                                                                                      |

|    | FREQ_OFFSET   | 31:24 | 0    | R   | Frequency offset.<br>Freq_offset(Hz) = 7812.5*FREQ_OFFSET                                                                                                     |

|    | DC_OOFSET_Q   | 23:16 | 0    | R   | DC offset for I path                                                                                                                                          |

|    | DC_OOFSET_I   | 15:8  | 0    | R   | DC offset for Q path                                                                                                                                          |

|    | PLOS_CNT[3:0] | 7:4   | 0000 | R   | Count lost packets. Overflow protected to 15, and stops at <b>maximum</b> value until reset. Counter reset by writing to RF_CH                                |

|    | ARC_CNT[3:0]  | 3:0   | 0000 | R   | Count retransmitted packets. Counter resets when transmission of a new packet starts                                                                          |

| 09 | RSSI          |       |      |     | TSSI and RSSI indicator/control                                                                                                                               |

|    | RSSIDB_OFFSET | 13:8  | 0    | R/W | RSSI(dBm) offst for RSSI calculate                                                                                                                            |

|    | Reserved      | 7     | 0    | R/W | Must be 0 for normal operation                                                                                                                                |

|    | Reserved      | 6     | 0    | R/W | Must be 0 for normal operation                                                                                                                                |

|    | Reserved      | 5     | 0    | R/W | Must be 0 for normal operation                                                                                                                                |

|    | EN_RSSI       | 4     | 0    | R/W | Enable RSSI                                                                                                                                                   |

|    | Reserved      | 3     | 0    | R   | Reserved register readout                                                                                                                                     |

|    | Reserved      | 2     | 0    | R   | Reserved register readout                                                                                                                                     |

|    | RSSI2         | 1     | 0    | R   | RSSI indicator at threshold 2                                                                                                                                 |

|    | RSSI1         | 0     | 0    | R   | RSSI indicator at threshold 1                                                                                                                                 |

|    |                |       |                  |     |                                                                                                                         |

|----|----------------|-------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 0A | RX_ADDR_P0     | 39:0  | 0xE7E7E7E7E<br>7 | R/W | RX address data pipe 0. 5 bytes<br><b>maximum</b> . LSB byte written first.<br>Number of bytes used set by<br>SETUP_AW. |

| 0B | RX_ADDR_P1     | 39:0  | 0xC2C2C2C2<br>C2 | R/W | RX address data pipe 1. 5 bytes<br><b>maximum</b> . LSB byte written first.<br>Number of bytes used set by<br>SETUP_AW. |

| 0C | RX_ADDR_P2TOP5 |       |                  |     | Only LSB are set, MSB bytes use<br>RX_ADDR_P1[39:8]                                                                     |

|    | RX_ADDR_P5     | 31:24 | 0xc6             | R/W | RX address data pipe 5.                                                                                                 |

|    | RX_ADDR_P4     | 23:16 | 0xc5             | R/W | RX address data pipe 4.                                                                                                 |

|    | RX_ADDR_P3     | 15:8  | 0xc4             | R/W | RX address data pipe 3.                                                                                                 |

|    | RX_ADDR_P2     | 7:0   | 0xc3             | R/W | RX address data pipe 2.                                                                                                 |

| 0D | BER_RESULT     |       |                  |     | BER(PN9) test result                                                                                                    |

|    | ERR_CNT        | 63:32 | 0x00             | R/W | Receive error Bit Counter                                                                                               |

|    | RECV_CNT       | 31:0  | 0x00             | R/W | Receive total Bit Counter                                                                                               |

| 0E | AGC_SETTING    |       |                  |     | AGC setting                                                                                                             |

|    | AGC_THRD_MAX   | 31:26 | 0xA              | R/W | AGC <b>maximum</b> threshold                                                                                            |

|    | AGC_THRD_MIN   | 25:20 | 0x3f             | R/W | AGC <b>minimum</b> threshold                                                                                            |

|    | AGC_GAIN_DELAY | 19:18 | 0x0              | R/W | Wait time after gain change;<br>0: 0.5us; 1: 1.0us; 2 1.5us; 3: 2.0us                                                   |

|    | ADC_RSSI_MEAN  | 17:16 | 0x0              | R/W | ADC RSSI calculate period;<br>0: 0.5us; 1: 1.0us; 2 1.5us; 3: 2.0us                                                     |

|    | AGC_MANU_SET   | 10:4  | 0x7b             | R/W | AGC manual setting                                                                                                      |

|    | AGC_ADJ_NUM    | 3:1   | 0x4              | R/W | AGC Gain adjust <b>maximum</b> number                                                                                   |

|    | AGC_MANU_EN    | 0     | 0                | R/W | AGC manual enable                                                                                                       |

| 0F | PGA_SETTING    |       |                  |     | PGA setting                                                                                                             |

|    | AGC_GAIN_5TH   | 38:32 | 0x30             | R/W | AGC 5th gain set                                                                                                        |

|    | AGC_GAIN_4TH   | 30:24 | 0x36             | R/W | AGC 4th gain set                                                                                                        |

|    | AGC_GAIN_3TH   | 22:16 | 0x3c             | R/W | AGC 3th gain set                                                                                                        |

|    | AGC_GAIN_2TH   | 14:8  | 0x42             | R/W | AGC 2th gain set                                                                                                        |

|    | AGC_GAIN_1TH   | 6:0   | 0x48             | R/W | AGC 1th gain set                                                                                                        |

| 10 | TX_ADDR        | 39:0  | 0xE7E7E7E7E<br>7 | R/W | TX address. Used for PTX only.<br>Set RX_ADDR_P0 equal to this<br>address to handle auto<br>acknowledgement             |

|    |                |       |                  |     |                                                                                                                         |

| 11 | RX_PW_PX       |       |                  |     |                                                                                                                         |

|    | Reserved       | 47:46 | 0                | R   | Unused                                                                                                                  |

|    | RX_PW_P5       | 45:40 | 0x20             | R/W | Number of bytes in RX payload in<br>data pipe 5 (1 to 32). 0: pipe not used                                             |

|    | Reserved       | 39:38 |                  | R   | Unused                                                                                                                  |

|    |             |       |                                                                                                                                                                                                             |     |                                                                          |

|----|-------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------|

|    | RX_PW_P4    | 37:32 | 0x20                                                                                                                                                                                                        | R/W | Number of bytes in RX payload in data pipe 4 (1 to 32). 0: pipe not used |

|    | Reserved    | 31:30 |                                                                                                                                                                                                             | R   | Unused                                                                   |

|    | RX_PW_P3    | 29:24 | 0x20                                                                                                                                                                                                        | R/W | Number of bytes in RX payload in data pipe 3 (1 to 32). 0: pipe not used |

|    | Reserved    | 23:22 |                                                                                                                                                                                                             | R   | Unused                                                                   |

|    | RX_PW_P2    | 21:16 | 0x20                                                                                                                                                                                                        | R/W | Number of bytes in RX payload in data pipe 2 (1 to 32). 0: pipe not used |

|    | Reserved    | 15:14 |                                                                                                                                                                                                             | R   | Unused                                                                   |

|    | RX_PW_P1    | 13:8  | 0x20                                                                                                                                                                                                        | R/W | Number of bytes in RX payload in data pipe 1 (1 to 32). 0: pipe not used |

|    | Reserved    | 7:6   |                                                                                                                                                                                                             | R   | Unused                                                                   |

|    | RX_PW_P0    | 5:0   | 0x20                                                                                                                                                                                                        | R/W | Number of bytes in RX payload in data pipe 0 (1 to 32). 0: pipe not used |

| 12 | ANALOG CFG0 | 127:0 | 01000111_11<br>111011_1110<br>1001_<br>01000000_00<br>010111_0100<br>1001_<br>00100100_00<br>000000_1101<br>0101_<br>11101010_00<br>001000_0000<br>0100_<br>00000000_00<br>000000_0000<br>0000_<br>00000000 | R/W | Analog register 0                                                        |

| 13 | ANALOG CFG1 | 127:0 | 10110000_00<br>101100_0000<br>0101_<br>10100000_11<br>110111_0001<br>1101_<br>10011000_01<br>000000_0000<br>0000_<br>00000111_10<br>000000_0001<br>0000_<br>00000000_00<br>000010_0100<br>1000_             | R/W | Analog register 1                                                        |

|    |                 |       |                                                                                                                                                                                                             |     |                                                                           |  |

|----|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------|--|

|    |                 |       | 11000000                                                                                                                                                                                                    |     |                                                                           |  |

| 14 | ANALOG CFG2     | 127:0 | 00000000_00<br>000000_0000<br>1101_<br>10010000_00<br>000000_0000<br>0000_<br>01000110_10<br>101010_0010<br>0111_<br>00100011_11<br>101111_0011<br>1010_<br>11011000_10<br>011010_1010<br>1100_<br>00000000 | R/W | Analog register 2                                                         |  |

| 15 | ANALOG CFG3     | 127:0 | 00110000_00<br>001100_0000<br>1000_<br>01101000_00<br>000000_0000<br>0000_<br>00011011_10<br>000000_0000<br>0001_<br>00110111_00<br>100100_1000<br>0101_<br>01101010_10<br>110010_0010<br>1110_<br>10011100 | R/W | Analog register 3                                                         |  |

| 17 | STATUS_FIFO     |       |                                                                                                                                                                                                             |     | FIFO status                                                               |  |

|    | BB_ANA3REG_7T3  | 19:15 | 0                                                                                                                                                                                                           | R   | Analog 3 register bit [7:3] from baseband register<br>1: calibration done |  |

|    | HW_RC_CL_DONE   | 14    | 0                                                                                                                                                                                                           | R   | Hardware RC Calibration done status<br>1: calibration done                |  |

|    | AD_RCCAL_FINISH | 13    | 0                                                                                                                                                                                                           | R   | RF status                                                                 |  |

|    | AD_RCCAL_CTRIM  | 12:8  | 0                                                                                                                                                                                                           | R   | RF status                                                                 |  |

|    |                      |       |          |   |                                                                                                                                                                                                                                                                                                                                    |

|----|----------------------|-------|----------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | PEND_RXFRM_NUM_H     | 7     | 0        | R | See PEND_RXFRM_NUM_L                                                                                                                                                                                                                                                                                                               |

|    | TX_REUSE             | 6     | 0        | R | Used for a PTX device<br>Pulse the rfce high for at least 10 $\mu$ s<br>to Reuse last<br>transmitted payload. TX payload<br>reuse is active<br>until W_TX_PAYLOAD or FLUSH<br>TX is executed.<br>TX_REUSE is set by the SPI<br>command<br>REUSE_TX_PL, and is reset by<br>the SPI commands<br>W_TX_PAYLOAD or FLUSH TX<br>*rewrite |

|    | TX_FULL              | 5     | 0        | R | 1: TX FIFO full 0: available slots in<br>TX FIFO                                                                                                                                                                                                                                                                                   |

|    | TX_EMPTY             | 4     | 1        | R | 1: TX FIFO empty 0: data in TX FIFO                                                                                                                                                                                                                                                                                                |

|    | PEND_RXFRM_NUM_L     | 3:2   | 0        | R | Total Rx frame number is pending in PRX<br>RXFIFO.<br>[PEND_RXFRM_NUM_H,<br>PEND_RXFRM_NUM_L]                                                                                                                                                                                                                                      |

|    | RX_FULL              | 1     | 0        | R | 1: RX FIFO full 0: available slots in<br>RX FIFO                                                                                                                                                                                                                                                                                   |

|    | RX_EMPTY             | 0     | 1        | R | 1: RX FIFO empty 0: RX FIFO full                                                                                                                                                                                                                                                                                                   |

| 18 | RSSIREC              |       |          |   | RSSI recorder feature                                                                                                                                                                                                                                                                                                              |

|    | Reserved             | 31:30 | 0x0      | R | Unused                                                                                                                                                                                                                                                                                                                             |

|    | RSSI_DBM             | 29:22 | 0x0      | R | RSSI(dBm) Calculate result                                                                                                                                                                                                                                                                                                         |

|    | RSSI2_VREF_SEL[2:0]  | 21:19 | 000      | W | RX RSSI VREF2 setting<br>000: -59 dBm, +4dB/step<br>111: out of range                                                                                                                                                                                                                                                              |

|    | RSSI1X_VREF_SEL[2:0] | 18:16 | 000      | W | RX RSSI VREF1 setting<br>000: -69 dBm, +4dB/step                                                                                                                                                                                                                                                                                   |

|    | RSSIREC2[7:0]        | 15:8  | 01110010 | R | RSSI2 recorder, MSB is most recent<br>recording, any write command on<br>this register will flush RSSI setting;<br>when RX_ON=0, PWR_ON=0 &<br>CE=0, register will<br>read chip ID                                                                                                                                                 |

|    | RSSIREC1[7:0]        | 7:0   | 01000001 | R | RSSI1 recorder, MSB is most recent<br>recording, any write command on<br>this register will flush RSSI setting;<br>when RX_ON=0, PWR_ON=0 &<br>CE=0, register will<br>read chip ID                                                                                                                                                 |

|    |                 |       |      |     |                                                                                                                                           |

|----|-----------------|-------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | TXPROC_CFG      |       |      |     | TX Process configuration                                                                                                                  |

|    | TXACK_WAIT_TIME | 28:25 | 0x4  | R/W | Tx ACK wait time after Rx Payload data for PRX<br>0: 0us<br>1: 7.5us<br>2. 15us<br>...<br>F: 112.5us                                      |

|    | MOD2DAC_CLKINV  | 24    | 0x0  | R/W | Mod2Dac clock output invert                                                                                                               |

|    | MOD2DAC_DLY     | 23:21 | 0x0  | R/W | Mod2Dac data delay cycle                                                                                                                  |

|    | KMOD_BPS        | 20    | 0x0  | R/W | Bypass KMOD coefficence                                                                                                                   |

|    | KMOD_SET        | 19:11 | 0x0  | R/W | KMOD coefficence Setting                                                                                                                  |

|    | GASFLT_BPS      | 10    | 0x0  | R/W | Bypass Gauss Filter                                                                                                                       |

|    | GASFLT_BT_SEL   | 9     | 0x0  | R/W | Gauss Filter BT Select<br>0: BT=0.5; 1: BT=1.0                                                                                            |

|    | FREQ_DEV        | 8:0   | 0xcd | R/W | Tx Deviation Frequecy                                                                                                                     |

| 1A | RXPROC_CFG      |       |      |     | RX Process configuration                                                                                                                  |

|    | RX_DEM_STARTCFG | 39    | 0x1  | R/W | 0: Disable RX Start Delay<br>1: Enable RX Start Delay                                                                                     |

|    | RX_DEM_START_DL | 38:32 | 0x20 | R/W | RX Start Delay counter at 16MHz                                                                                                           |

|    | PRE_DC_SET      | 31:24 | 0x0  | R/W | Freq offset manual set                                                                                                                    |

|    | MAX_FREQ        | 23:16 | 0x43 | R/W | Max Freq set for IPPLS                                                                                                                    |

|    | PRE_DC_WIND     | 15:14 | 0x1  | R/W | Freq offset calculate windows<br>0: final 2 preamble bit<br>1: final 4 preamble bit<br>2: final 6 preamble bit<br>3: final 8 preamble bit |

|    | SYNC_WIND_CFG   | 13:8  | 0x24 | R/W | Syncword search windows                                                                                                                   |

|    | CHAN_FLT_BPS    | 7     | 0x0  | R/W | Bypass channel filter                                                                                                                     |

|    | IPPLS_BPS       | 6     | 0x1  | R/W | Bypass IPPLS                                                                                                                              |

|    | PRE_DC_MANU     | 5     | 0x0  | R/W | Freq offset manual setting enable                                                                                                         |

|    | BER_HOLD        | 4     | 0x0  | R/W | Ber hold                                                                                                                                  |

|    | Reserved        | 3     | 0x0  | R/W | Unused                                                                                                                                    |

|    | DCFLT_BPS       | 2     | 0x0  | R/W | Bypass DC offset calculate                                                                                                                |

|    | ADC_SMP_PHA     | 1     | 0x1  | R/W | IF ADC data sample edge select;<br>1: inv                                                                                                 |

|    | RX_IQ_SWAP      | 0     | 0x0  | R/W | IF ADC data IQ swap                                                                                                                       |

| 1C | DYNPD           |       |      |     | Dynamic payload length                                                                                                                    |

|    | Reserved        | 7:6   | 00   | R/W | Unused                                                                                                                                    |

|    | DPL_P5          | 5     | 0    | R/W | Set 1 to enable dynamic payload length data pipe 5 (requires EN_DPL & ENAA_P5)                                                            |

|    |                  |       |      |     |                                                                                                                                                                                                                                                                       |

|----|------------------|-------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | DPL_P4           | 4     | 0    | R/W | Set 1 to enable dynamic payload length data pipe 4 (requires EN_DPL & ENAA_P4)                                                                                                                                                                                        |

|    | DPL_P3           | 3     | 0    | R/W | Set 1 to enable dynamic payload length data pipe 3 (requires EN_DPL & ENAA_P3)                                                                                                                                                                                        |

|    | DPL_P2           | 2     | 0    | R/W | Set 1 to enable dynamic payload length data pipe 2 (requires EN_DPL & ENAA_P2)                                                                                                                                                                                        |

|    | DPL_P1           | 1     | 0    | R/W | Set 1 to enable dynamic payload length data pipe 1 (requires EN_DPL & ENAA_P1)                                                                                                                                                                                        |

|    | DPL_P0           | 0     | 0    | R/W | Set 1 to enable dynamic payload length data pipe 0 (requires EN_DPL & ENAA_P0)                                                                                                                                                                                        |

| 1D | FEATURE          |       |      |     | Features                                                                                                                                                                                                                                                              |

|    | STAT_SETUP [1:0] | 7:6   | 00   | R/W | Adjust the output of SDO during command input<br>00: default, SDO output is STATUS<br>01: RX readout mode, the SDO output MAX_RT and TX_FULL bit is replaced by RSSI1 and RSSI2 readout<br>10: FIFO readout mode, SDO output is STATUS_FIFO<br>11: unused, same as 00 |

|    | EN_LONG_PLD      | 5     | 0    | R/W | Set 1 enables long payload feature max length is 128Byte                                                                                                                                                                                                              |

|    | EN_FEC           | 4     | 1    | R/W | Set 1 enable FEC&Interleave feature                                                                                                                                                                                                                                   |

|    | EN_WHITEN        | 3     | 1    | R/W | Set 1 enable whiten feature                                                                                                                                                                                                                                           |

|    | EN_DPL           | 2     | 1    | R/W | Set 1 enables dynamic payload length                                                                                                                                                                                                                                  |

|    | EN_ACK_PAY       | 1     | 0    | R/W | Set 1 enables payload on ACK                                                                                                                                                                                                                                          |

|    | EN_DYN_ACK       | 0     | 0    | R/W | Set 1 enables the W_TX_PAYLOAD_NOACK command                                                                                                                                                                                                                          |

| 1E | RAMP_CFG         |       |      |     | PA Ramp Configuration                                                                                                                                                                                                                                                 |

|    | RAMP_14TH        | 87:82 | 0x3b | R/W | PA 14th ramp value                                                                                                                                                                                                                                                    |

|    | RAMP_13TH        | 81:76 | 0x37 | R/W | PA 13th ramp value                                                                                                                                                                                                                                                    |

|    | RAMP_12TH        | 75:70 | 0x33 | R/W | PA 12th ramp value                                                                                                                                                                                                                                                    |

|    | RAMP_11TH        | 69:64 | 0x2e | R/W | PA 11th ramp value                                                                                                                                                                                                                                                    |

|    | RAMP_10TH        | 63:58 | 0x2a | R/W | PA 10th ramp value                                                                                                                                                                                                                                                    |

|    | RAMP_9TH         | 57:52 | 0x26 | R/W | PA 9th ramp value                                                                                                                                                                                                                                                     |

|    | RAMP_8TH         | 51:46 | 0x22 | R/W | PA 8th ramp value                                                                                                                                                                                                                                                     |

|    | RAMP_7TH         | 45:40 | 0x1d | R/W | PA 7th ramp value                                                                                                                                                                                                                                                     |

|  |           |       |      |     |                                                       |

|--|-----------|-------|------|-----|-------------------------------------------------------|

|  | RAMP_6TH  | 39:34 | 0x19 | R/W | PA 6th ramp value                                     |

|  | RAMP_5TH  | 33:28 | 0x15 | R/W | PA 5th ramp value                                     |

|  | RAMP_4TH  | 27:22 | 0x11 | R/W | PA 4th ramp value                                     |

|  | RAMP_3TH  | 21:16 | 0xc  | R/W | PA 3th ramp value                                     |

|  | RAMP_2TH  | 15:10 | 0x8  | R/W | PA 3th ramp value                                     |

|  | RAMP_1TH  | 9:4   | 0x4  | R/W | PA 1th ramp value                                     |

|  | RAMP_TIME | 2:0   | 0x0  | R/W | Ramp time;<br>0: 7.5us<br>1: 15us<br>...<br>7: 52.5us |

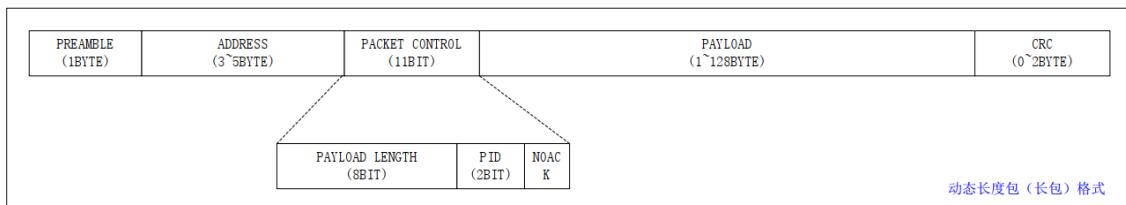

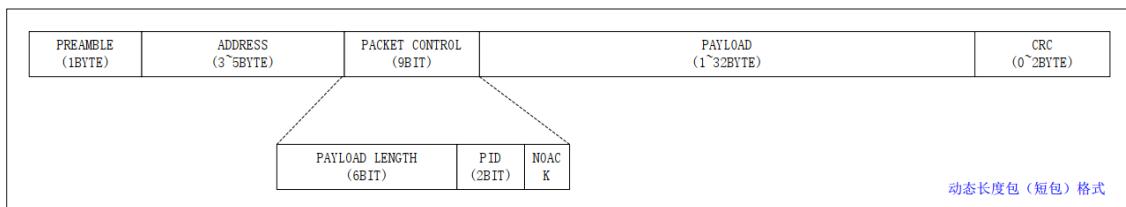

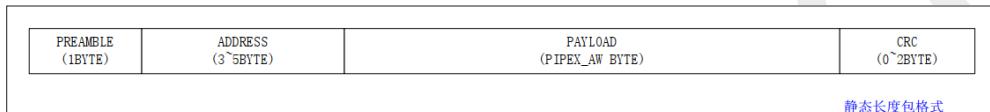

## 11 数据包格式描述

如上图所示，系统支持 3 种包格式：

1. 静态长度包。固定长度包，包长度由收发双方协商确定。

2. 动态长度包（短包）格式，支持最大包长度为 32byte，该模式下系统可以最多缓存 4 个包。需使能 FEATURE 寄存器中的 EN\_DPL。

3. 动态长度包（长包）格式，支持最大包长度为 128byte。使用长包模式需要使能 FEATURE 寄存器中的 EN\_DPL 和 EN\_LONG\_PLD，且该模式下系统只能缓存 1 个包

注：BLE 广播包配置会有点区别，我们会提供驱动软件包。

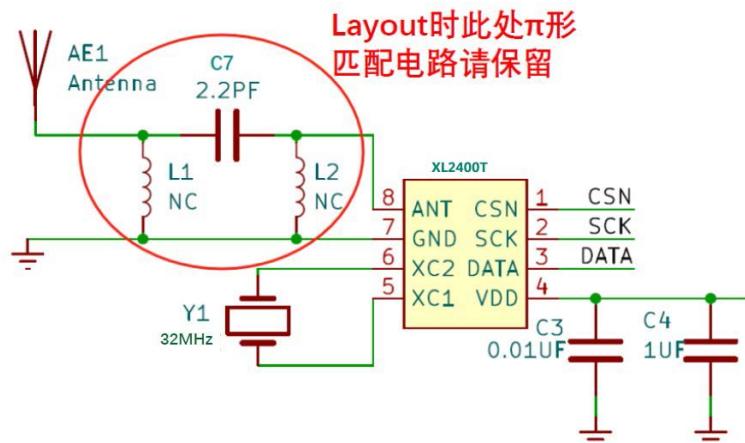

## 12 典型应用电路 (参考)

\*注 1: 芯片的 NC 引脚可以悬空;

\*注 2: 外围元器件备注;

| 物料编号 | 备注                                 |

|------|------------------------------------|

| C3   | 10nF                               |

| C4   | 1uF                                |

| C2   | 推荐 2.2pF, 可选择范围在 1.5~3pF           |

| Y1   | 32MHz & C <sub>L</sub> =12pF 10ppm |

\*注3: Layout时天线使用 π 形匹配电路, C1\L1\L2, 方便根据板子调整RF性能;

\*注 4: VDD 供电电压严格控制在 3.6V 以下;

## 13 PCB设计指导（参考）

- VCC脚滤波电容最好是越靠近IC管脚位越好。

- XL2400T 对电源要求较高，必须保证供电的稳定，电源尽量星形布线，除天线部分外，其它部分全部铺地，铺地连接尽量完整。

- 晶振尽量靠近IC管脚。

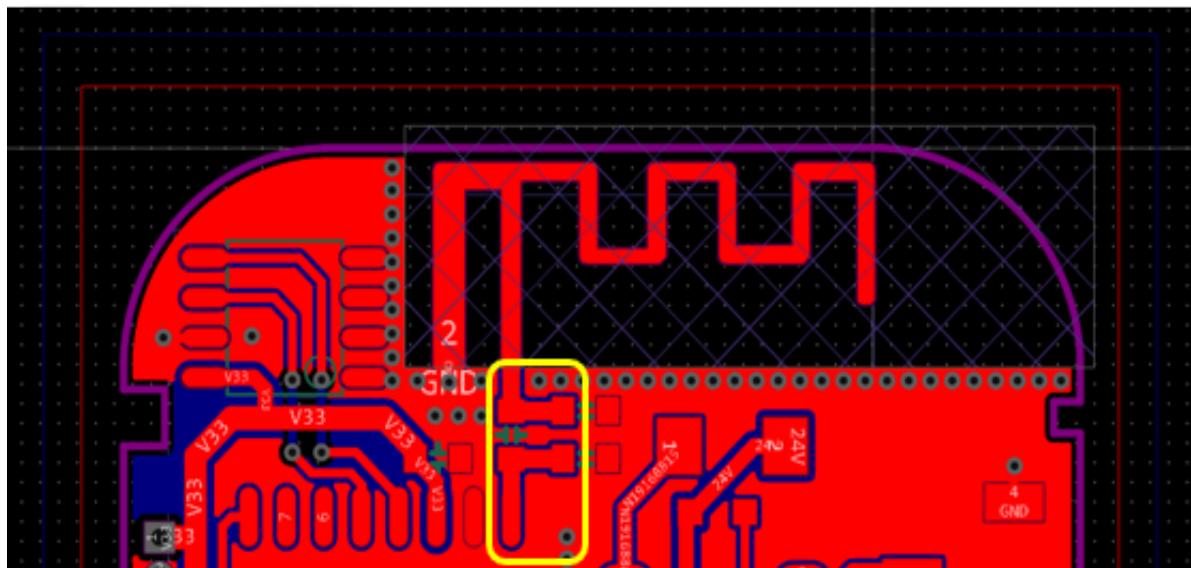

- 射频设计要求微带线需要进行阻抗匹配（即微带线的线宽与和GND的间距要限制），并且要求使用GND铺铜将整个微带线在平面上包住且固定间距打GND孔，以达到屏蔽干扰和EMC/EMI的作用。

- 微带线周围尽量不要存在其他的线路穿插或并行，减小射频干扰。

- 天线部分净空区边缘位置需要固定间距打GND孔，防止天线发射出的信号被反射回板内，对芯片造成干扰。

- 微带线需要尽可能短，用以减小因线长导致的信号衰减，简称线损。

- 微带线线宽建议0.8mm, 线距建议0.254mm(双层板),

- 微带线即从芯片射频脚到天线起始点这一截线路（下图黄色框参考所示）。

## 14 印制天线设计（参考）

### 14.1 印制板天线layout 设计

2.4G 的印制版天线主要有两种结构，PIFA 天线和单级天线。PIFA 天线的天线馈电点和地点是连接到一起的，天线和地之间形成一个电容效应，就是信号通过天线（等效为电感）升压到等效电容上，通过电容再把能量辐射。单级天线是采用 1/4 波长原理，其中一个馈点是螺旋或者单杆，另外一极是地。两种天线的场结构简单，可以简单等效为一个 LC 谐振回路，其中 C 特别小，一个一个的谐振回路耦合上去，最后电磁场释放到外部。

PIFA 天线的电容相对于单级天线来说大很多，也就是说能量在谐振腔中更多，外界不容易干扰，也很难改变 PIFA 天线的阻抗，所以稳定性比单级天线强；但也因为他的电容太大，导致外界的相同的能量进入，在 PIFA 天线上产生的电压变化，远远不如单级天线大。所以效率和灵敏度低于单级天线。

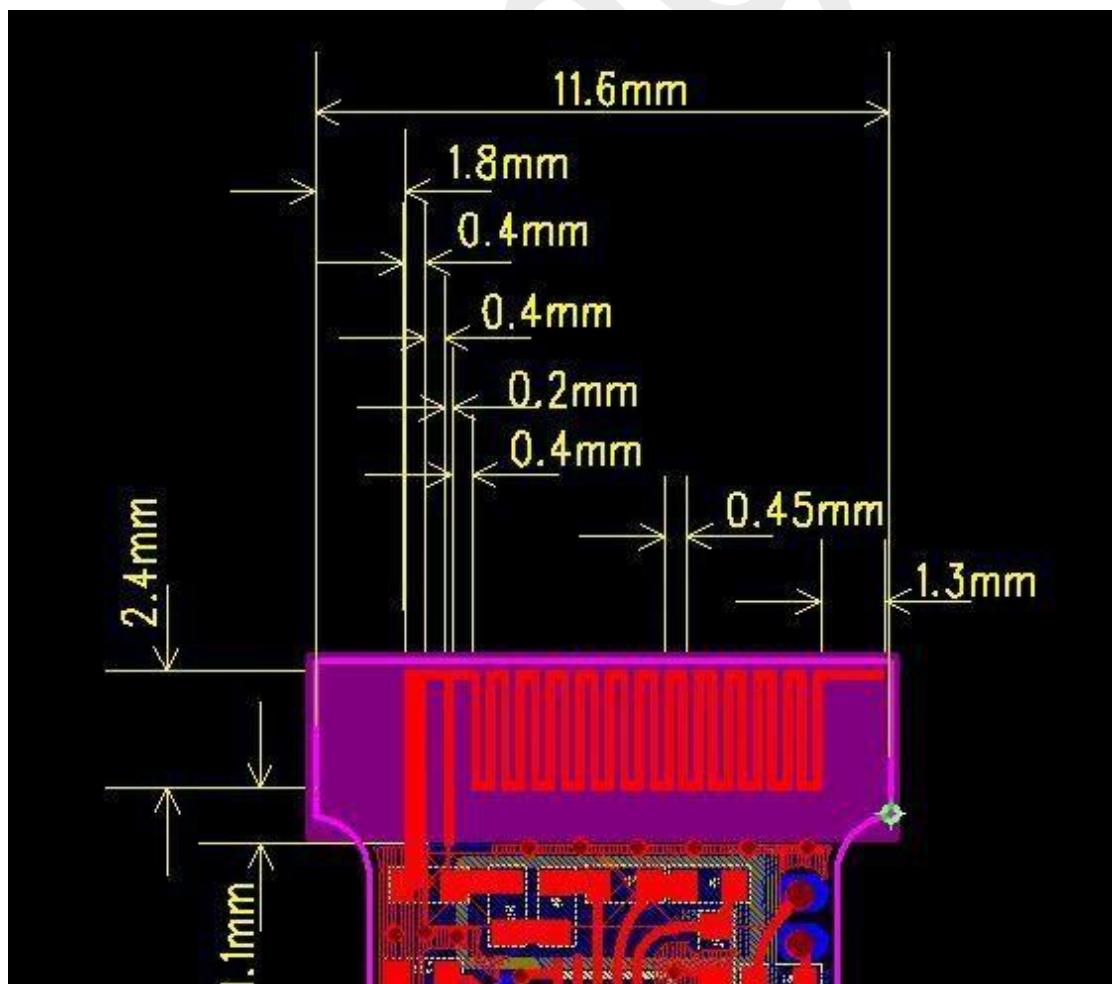

### 14.2 Dongle 端的PIFA 天线设计

Nano Dongle 天线采用超小型的 PIFA 天线，由于 PCB 面积受限，该天线的增益会比其他天线小，对通信距离会有影响，一般通信距离可以达到 15-20 米左右。天线具体尺寸如下图所示。天线的增益最大增益为-0.5dB 。

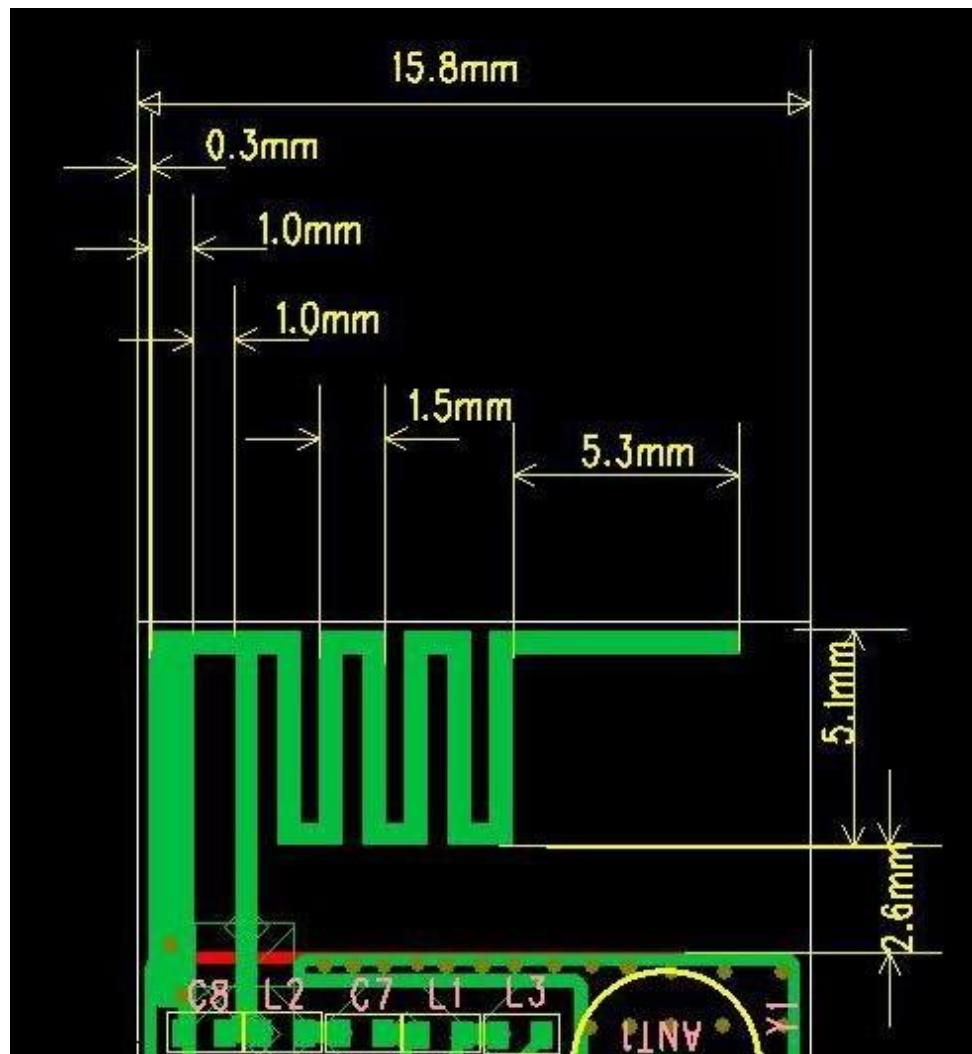

## 14.3 遥控器控制板的中尺寸 PIFA 天线设计

遥控器控制板的中尺寸PIFA 天线尺寸下图所示，天线的最大增益为 0.9dB。

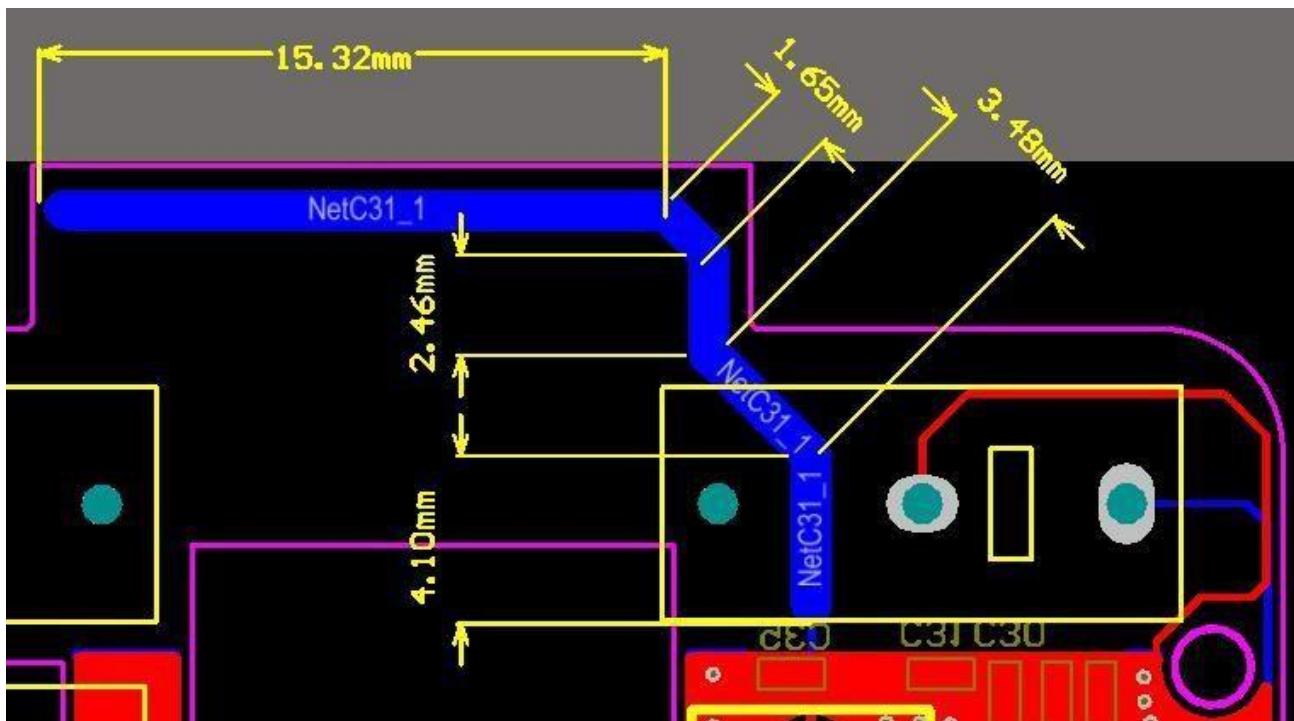

## 14.4 无线鼠标板及遥控器的单极天线设计

无线鼠标板的单极天线，增益较大，走线灵活，在有足够的 PCB 空间的情况下可以使用。在设计天线位置时，天线放置在无线鼠标板的前部或者左前部，减少右手握住鼠标的情况下手对辐射功率的吸收和衰减，该天线也可以应用到遥控器上；并且根据产品外形可以稍微更改天线的走线形状。参考尺寸如下图所示，天线的最大增益为 3.7dB。

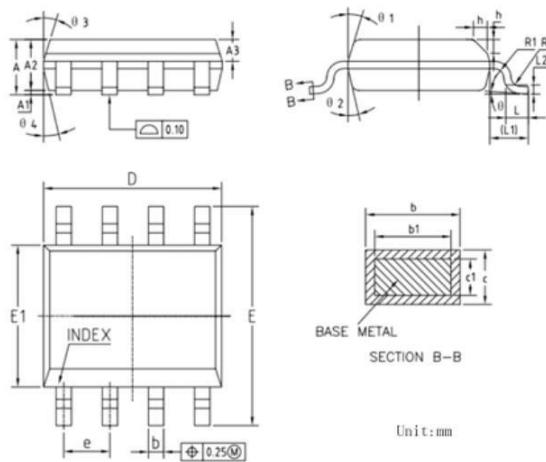

## 14 芯片封装信息

本芯片采用 SOP8 封装方式，具体封装尺寸信息如下：

SOP-8 封装尺寸如下：

| SYMBOL | MIN     | NOM  | MAX  |

|--------|---------|------|------|

| A      | 1.35    | 1.55 | 1.75 |

| A1     | 0.10    | 0.15 | 0.25 |

| A2     | 1.25    | 1.40 | 1.65 |

| A3     | 0.50    | 0.60 | 0.70 |

| b      | 0.38    | —    | 0.51 |

| b1     | 0.37    | 0.42 | 0.47 |

| c      | 0.17    | —    | 0.25 |

| c1     | 0.17    | 0.20 | 0.23 |

| D      | 4.80    | 4.90 | 5.00 |

| E      | 5.80    | 6.00 | 6.20 |

| E1     | 3.80    | 3.90 | 4.00 |

| e      | 1.27BSC |      |      |

| L      | 0.45    | 0.60 | 0.80 |

| L1     | 1.04REF |      |      |

| L2     | 0.25BSC |      |      |

| R      | 0.07    | —    | —    |

| R1     | 0.07    | —    | —    |

| h      | 0.30    | 0.40 | 0.50 |

| θ      | 0°      | —    | 8°   |

| θ 1    | 15°     | 17°  | 19°  |

| θ 2    | 11°     | 13°  | 15°  |

| θ 3    | 15°     | 17°  | 19°  |

| θ 4    | 11°     | 13°  | 15°  |

## 15 注意事项

- **接地：**金属底板采用尽量多的通孔接地，减小寄生电感。

- **电源旁路：**为了器件能很好工作，电源引线处建议用  $0.1\mu F$  电容滤波，电容需靠近器件。

- **防静电损伤：**器件为静电敏感器件，传输、装配、测试过程中应采取充分的防静电措施。

- 用户在使用前应进行外观检查，电路底部、侧面、四周光亮方可进行焊接。如 现氧化可采用去氧化手段对电路进行处理，处理完成电路必须在 4 小时内完成焊接。

- 包装袋被打开后，元器件将被回流焊制程或其他的高温制程所采用时必须符合：

- a) 在 12 小时内且工厂环境为温度  $< 30^{\circ}C$ ，湿度  $\leq 60\%RH$  完成；

- b) 使用前需进行去湿处理（建议  $125^{\circ}C$ ，4 小时烘烤）。

- 生产贴片的最高炉温为  $245^{\circ}C$ 。

- 产品说明书以发布日期为准，适时修改不另行说明。

## 16 防护注意事项

- 产品必须进行密封真空包装，并建议放置在干燥柜中储存，在温度小于 30°C 且湿度小于 60% 时，可达 12 个月。

- 打开包装后，如未使用完，则剩余产品需进行抽真空并放置在干燥柜中保管。超期产品使用前必须进行去湿和去氧化处理。

Xinlinggo